RACAL Instruments

#### PUBLICATION DATE: February 20, 2003

Copyright 2003 by Racal Instruments, Inc. Printed in the United States of America. All rights reserved. This book or parts thereof may not be reproduced in any form without written permission of the publisher.

#### THANK YOU FOR PURCHASING THIS RACAL INSTRUMENTS PRODUCT.

For this product, or any other Racal Instruments product that incorporates software drivers, you may access our web site to verify and/or download the latest driver versions. The web address for driver downloads is:

#### http://www.racalinstruments.com/downloads

You will be asked to register one time only to gain access to the driver and product manual downloads sections. At registration a cookie will be placed on your computer if you choose to accept it. This is done to facilitate your use of these sections on future visits. You may refuse to accept the cookie and still have complete access to the software driver database but will have to re-register every time you visit. This cookie is for ease of use only and no information is gathered for, sold, or reported to, any third party organization.

If you have any questions about software driver downloads or our privacy policy, please contact us at info@racalinstruments.com.

#### WARRANTY STATEMENT

All Racal Instruments, Inc. products are designed and manufactured to exacting standards and in full conformance to Racal's ISO 9001 procedures.

For the specific terms of your standard warranty, or optional extended warranty or service agreement, contact your Racal customer service advisor. Please have the following information available to facilitate service.

- 1. Product serial number

- 2. Product model number

- 3. Your company and contact information

You may contact your customer service advisor by:

| E-Mail:    | Helpdesk@racalinstruments.com                           |                              |

|------------|---------------------------------------------------------|------------------------------|

| Telephone: | +1 800 722 3262<br>+44(0) 8706 080134<br>+852 2405 5500 | (USA)<br>(UK)<br>(Hong Kong) |

| Fax:       | +1 949 859 7309<br>+44(0) 1628 662017<br>+852 2416 4335 | (USA)<br>(UK)<br>(Hong Kong) |

#### **RETURN of PRODUCT**

Authorization is required from Racal Instruments before you send us your product for service or calibration. Call your nearest Racal Instruments support facility. A list is located on the last page of this manual. If you are unsure where to call, contact Racal Instruments, Inc. Customer Support Department in Irvine, California, USA at 1-800-722-3262 or 1-949-859-8999 or via fax at 1-949-859-7139. We can be reached at: <u>helpdesk@racalinstruments.com</u>.

### **PROPRIETARY NOTICE**

This document and the technical data herein disclosed, are proprietary to Racal Instruments, and shall not, without express written permission of Racal Instruments, be used, in whole or in part to solicit quotations from a competitive source or used for manufacture by anyone other than Racal Instruments. The information herein has been developed at private expense, and may only be used for operation and maintenance reference purposes or for purposes of engineering evaluation and incorporation into technical specifications and other documents which specify procurement of products from Racal Instruments.

#### DISCLAIMER

Buyer acknowledges and agrees that it is responsible for the operation of the goods purchased and should ensure that they are used properly and in accordance with this handbook and any other instructions provided by Seller. RII products are not specifically designed, manufactured or intended to be used as parts, assemblies or components in planning, construction, maintenance or operation of a nuclear facility, or in life support or safety critical applications in which the failure of the RII product could create a situation where personal injury or death could occur. Should Buyer purchase RII product for such unintended application, Buyer shall indemnify and hold RII, its officers, employees, subsidiaries, affiliates and distributors harmless against all claims arising out of a claim for personal injury or death associated with such unintended use.

# FOR YOUR SAFETY

Before undertaking any troubleshooting, maintenance or exploratory procedure, read carefully the **WARNINGS** and **CAUTION** notices.

This equipment contains voltage hazardous to human life and safety, and is capable of inflicting personal injury.

If this instrument is to be powered from the AC line (mains) through an autotransformer, ensure the common connector is connected to the neutral (earth pole) of the power supply.

Before operating the unit, ensure the conductor (green wire) is connected to the ground (earth) conductor of the power outlet. Do not use a two-conductor extension cord or a three-prong/two-prong adapter. This will defeat the protective feature of the third conductor in the power cord.

Maintenance and calibration procedures sometimes call for operation of the unit with power applied and protective covers removed. Read the procedures and heed warnings to avoid "live" circuit points.

Before operating this instrument:

- 1. Ensure the proper fuse is in place for the power source to operate.

- 2. Ensure all other devices connected to or in proximity to this instrument are properly

grounded or connected to the protective third-wire earth ground. If the instrument:

- fails to operate satisfactorily

- shows visible damage

- has been stored under unfavorable conditions

- has sustained stress

Do not operate until, performance is checked by qualified personnel.

## **Racal Instruments**

#### **EC Declaration of Conformity**

| We |                                  |                                                                                                                                                                |

|----|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 4 Go                             | al Instruments Inc.<br>odyear Street<br>e, CA 92718                                                                                                            |

|    | declare und                      | er sole responsibility that the                                                                                                                                |

|    | 6075-4, 4 C<br>P/N 407840<br>and | hannel Serial Communications Module<br>I-004                                                                                                                   |

|    | 6075-8, 8 C<br>P/N 407840        | hannel Serial Communications Module<br>0-008                                                                                                                   |

|    | conform to                       | the following Product Specifications:                                                                                                                          |

|    | Safety:                          | EN61010-1:1993+A2:1995                                                                                                                                         |

|    | EMC:                             | EN61326:1997+A1:1998                                                                                                                                           |

|    | Supplemer                        | ntary Information:                                                                                                                                             |

|    | insta<br>with                    | above specifications are met when the product is<br>lled in a Racal Instruments certified mainframe<br>faceplates installed over all unused slots, as<br>cable |

|    | of th                            | product herewith complies with the requirements<br>e Low Voltage Directive 73/23/EEC and the EMC<br>ctive 89/336/EEC.                                          |

|    | Irvine, CA,                      | December 23, 2002 <u>Faum Kunsu</u><br>Karen Evensen, Engineering Director                                                                                     |

#### TABLE OF CONTENTS

| Chapter 1                                     | 1-1  |

|-----------------------------------------------|------|

| GETTING STARTED                               | 1-1  |

| What's In This Chapter                        | 1-1  |

| VXIbus Description                            | 1-3  |

| Safety Considerations                         | 1-7  |

| Supplied Accessories                          | 1-8  |

| Specifications                                | 1-8  |

| Functional Description                        | 1-16 |

| Chapter 2                                     | 2-1  |

| CONFIGURING THE INSTRUMENT                    | 2-1  |

| Installation Overview                         | 2-1  |

| Unpacking and Initial Inspection              | 2-1  |

| Safety Precautions                            | 2-1  |

| Performance Checks                            | 2-2  |

| Grounding Requirements                        | 2-2  |

| Long Term Storage or Repackaging For Shipment | 2-2  |

| Preparation For Use                           | 2-3  |

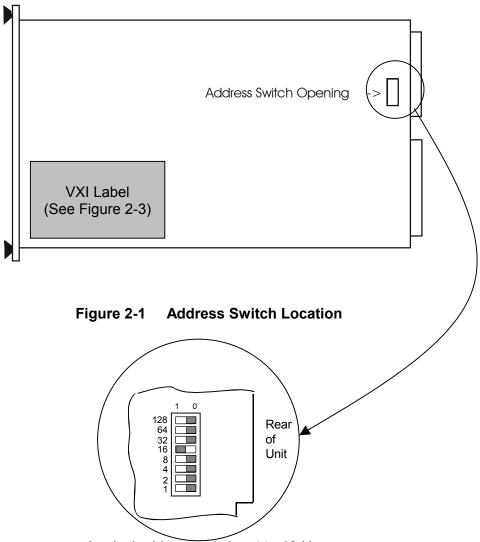

| Logical Address Selection                     | 2-3  |

| VXI Labeling                                  | 2-4  |

| Checking the 6075's Logical Device Address    | 2-5  |

| Serial Interface                              | 2-5  |

| Four Channel Units                            | 2-5  |

| RS-232 Connections                            | 2-6  |

| RS-422 Connections                            | 2-7  |

| RS-485 Connections                            | 2-7  |

| Eight Channel Units                           | 2-7  |

| Chapter 3                                     | 3-1  |

| USING THE INSTRUMENT                          | 3-1  |

| Overview                                      | 3-1  |

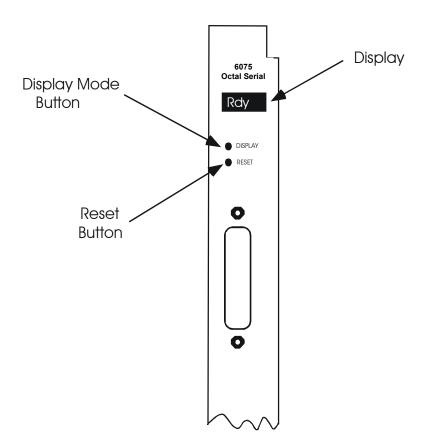

| Front Panel Displays and Controls             | 3-1  |

| Alphanumeric Display                          | 3-1  |

| Display Button                                |      |

| Reset Button                                  |      |

| Display Modes                                 | 3-3  |

| Pre-Operation Setup       3-4         Power Turn-on       3-5         Interface Programming Concepts       3-5         Program Recommendations       3-7         Controlling the 6075 with Multi-Tasking Operating Systems       3-7         Word Serial Commands       3-8         Fast Data Channel Usage       3-10         6075 FDC Buffer Organization       3-10         FDC Buffer Definitions       3-12         FDC Buffer Operation       3-13         FDC Buffer Operation       3-13         488.2 Compliance       3-14         488.2 Compliance       3-14         488.2 Compliance       3-14         488.2 Status Reporting Structure       3-14         488.2 Compliance       3-16         Questionable Registers       3-17         Operational Condition Registers       3-17         Output Queue       3-18         Status Byte Register Values       3-20         SCPI Conformance Information       3-22         Programming Guidelines       3-28         Overview       3-28         VXI Programming Requirements       3-28         VXI Programming Requirements       3-22         SDLC Mode Operation       3-33 | General Operating Instructions                            |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------|

| Interface Programming Concepts.3-5Program Recommendations3-7Controlling the 6075 with Multi-Tasking Operating Systems.3-7Word Serial Commands3-8Fast Data Channel Usage3-106075 FDC Buffer Organization3-10FDC Buffer Definitions3-12FDC Buffer Definitions3-13FDC Buffer Initialization3-13FDC Buffer Organization3-13FDC Buffer Operation3-13488.2 Compliance3-14488.2 Status Reporting Structure3-14Event Registers3-16Standard Event Status Register3-16Questionable Registers3-17Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Status Byte Register Values3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28Overview3-28VXI Programming Requirements3-20SDLC Mode Operation3-31Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-33Timing Pulse Output3-33Clock Selection3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                        | Pre-Operation Setup                                       |      |

| Program Recommendations3-7Controlling the 6075 with Multi-Tasking Operating Systems3-7Word Serial Commands3-8Fast Data Channel Usage3-106075 FDC Buffer Organization3-10FDC Buffer Definitions3-12FDC Buffer Operation3-13FDC Buffer Operation3-13FDC Buffer Operation3-13488.2 Compliance3-14488.2 Status Reporting Structure3-16Standard Event Status Register3-16Questionable Registers3-17Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Saving the Enable Register Values3-20SCPI Conformance Information3-22Programming Guidelines3-28Overview3-28VXI Programming Requirements3-28Transmitting Data3-30Receiving Data3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                | Power Turn-on                                             | 3-5  |

| Controlling the 6075 with Multi-Tasking Operating Systems.3-7Word Serial Commands3-8Fast Data Channel Usage3-106075 FDC Buffer Organization3-10FDC Buffer Organization3-11FDC Buffer Initialization3-13FDC Buffer Operation3-13FDC Buffer Operation3-13488.2 Compliance3-14488.2 Status Reporting Structure3-14Event Registers3-16Standard Event Status Register3-16Questionable Registers3-17Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Saving the Enable Register Values3-20SCPI Conformance Information3-22Programming Guidelines3-28VXI Programming Requirements3-28VXI Programming Requirements3-28VXI Programming Requirements3-28Testing an Asynchronous Channel3-29Transmitting Data3-30Receiving Messages with an EOM Character3-33SDLC Mode Operation3-33Timing Pulse Output3-33Clock Selection3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                              | Interface Programming Concepts                            | 3-5  |

| Word Serial Commands3-8Fast Data Channel Usage3-106075 FDC Buffer Organization3-10FDC Buffer Organization3-12FDC Buffer Initialization3-13FDC Buffer Operation3-13488.2 Compliance3-14488.2 Status Reporting Structure3-14Event Registers3-16Standard Event Status Register3-16Questionable Registers3-17Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Status Byte Register Values3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28VXI Programming Requirements3-28VXI Programming Requirements3-28Testing an Asynchronous Channel3-21Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                               | Program Recommendations                                   | 3-7  |

| Fast Data Channel Usage3-106075 FDC Buffer Organization3-10FDC Buffer Definitions3-12FDC Buffer Initialization3-13FDC Buffer Operation3-13488.2 Compliance3-14488.2 Status Reporting Structure3-14Event Registers3-16Standard Event Status Register3-16Questionable Registers3-17Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Status Byte Register Values3-20SCPI Conformance Information3-22Programming Guidelines3-28Overview3-28VXI Programming Requirements3-28Transmitting Data3-30Receiving Messages with an EOM Character3-32SDLC Mode Operation3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Controlling the 6075 with Multi-Tasking Operating Systems | 3-7  |

| 6075 FDC Buffer Organization3-10FDC Buffer Definitions3-12FDC Buffer Initialization3-13FDC Buffer Operation3-13488.2 Compliance3-14488.2 Status Reporting Structure3-14Event Registers3-16Standard Event Status Register3-17Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Status Byte Register3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28Overview3-28VXI Programming Requirements3-29Transmitting Data3-30Receiving Messages with an EOM Character3-32SDLC Mode Operation3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Word Serial Commands                                      | 3-8  |

| FDC Buffer Definitions3-12FDC Buffer Initialization3-13FDC Buffer Operation3-13488.2 Compliance3-14488.2 Status Reporting Structure3-14Event Registers3-16Standard Event Status Register3-16Questionable Registers3-17Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Saving the Enable Register Values3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28VXI Programming Requirements3-28Testing an Asynchronous Channel3-29Transmitting Data3-30Receiving Messages with an EOM Character3-32SDLC Mode Operation3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Fast Data Channel Usage                                   | 3-10 |

| FDC Buffer Initialization3-13FDC Buffer Operation3-13488.2 Compliance3-14488.2 Status Reporting Structure3-14Event Registers3-16Standard Event Status Register3-16Questionable Registers3-17Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Status Byte Register3-18Status Byte Register3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28VXI Programming Requirements3-28VXI Programming Requirements3-29Transmitting Data3-30Receiving Messages with an EOM Character3-33SDLC Mode Operation3-33Timing Pulse Output3-33Chapter 4.4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6075 FDC Buffer Organization                              | 3-10 |

| FDC Buffer Operation3-13488.2 Compliance3-14488.2 Status Reporting Structure3-14Event Registers3-16Standard Event Status Register3-16Questionable Registers3-17Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Status Byte Register3-18Status Byte Register3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28VXI Programming Requirements3-28VXI Programming Requirements3-29Transmitting Data3-30Receiving Messages with an EOM Character3-33SDLC Mode Operation3-33Timing Pulse Output3-33Chapter 4.4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FDC Buffer Definitions                                    |      |

| 488.2 Compliance3-14488.2 Status Reporting Structure3-14Event Registers3-16Standard Event Status Register3-16Questionable Registers3-17Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Status Byte Register3-18Saving the Enable Register Values3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28VXI Programming Requirements3-28VXI Programming Requirements3-29Transmitting Data3-31Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-33Clock Selection3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FDC Buffer Initialization                                 | 3-13 |

| 488.2 Status Reporting Structure3-14Event Registers3-16Standard Event Status Register3-16Questionable Registers3-17Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Saving the Enable Register Values3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28VXI Programming Requirements3-28VXI Programming Requirements3-29Transmitting Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | FDC Buffer Operation                                      | 3-13 |

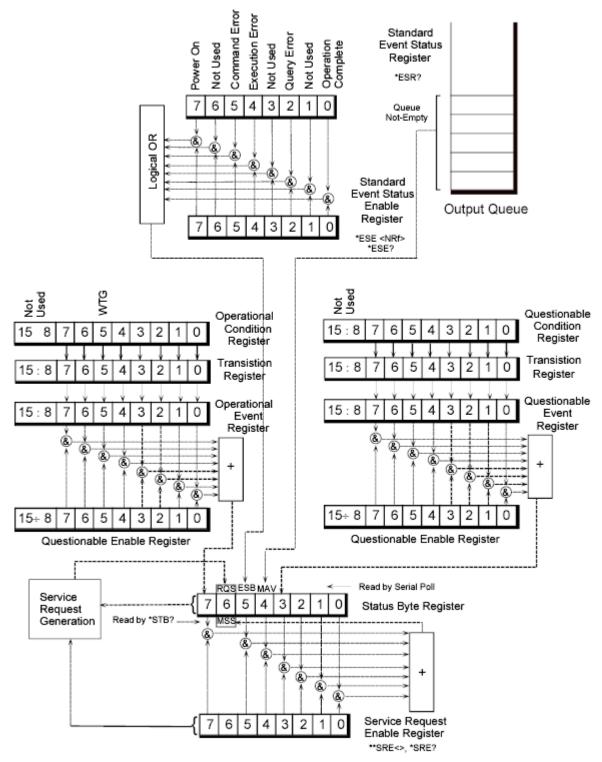

| Event Registers.3-16Standard Event Status Register3-16Questionable Registers.3-17Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Saving the Enable Register Values3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28VXI Programming Requirements3-28VXI Programming Requirements3-29Transmitting Data3-30Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 488.2 Compliance                                          | 3-14 |

| Standard Event Status Register3-16Questionable Registers3-17Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Saving the Enable Register Values3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28Overview3-28VXI Programming Requirements3-29Transmitting Data3-30Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 488.2 Status Reporting Structure                          | 3-14 |

| Questionable Registers3-17Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Saving the Enable Register Values3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28Overview3-28VXI Programming Requirements3-29Transmitting Data3-30Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Event Registers                                           |      |

| Operational Condition Registers3-17Output Queue3-18Status Byte Register3-18Saving the Enable Register Values3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28Overview3-28VXI Programming Requirements3-29Transmitting Data3-30Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-33Clock Selection3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Standard Event Status Register                            | 3-16 |

| Output Queue3-18Status Byte Register3-18Saving the Enable Register Values3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28Overview3-28VXI Programming Requirements3-28Testing an Asynchronous Channel3-29Transmitting Data3-31Receiving Data3-32SDLC Mode Operation3-32Clock Selection3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Questionable Registers                                    | 3-17 |

| Status Byte Register3-18Saving the Enable Register Values3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28Overview3-28VXI Programming Requirements3-28Testing an Asynchronous Channel3-29Transmitting Data3-30Receiving Messages with an EOM Character3-32SDLC Mode Operation3-32Clock Selection3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Operational Condition Registers                           | 3-17 |

| Saving the Enable Register Values3-20SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28Overview3-28VXI Programming Requirements3-28Testing an Asynchronous Channel3-29Transmitting Data3-30Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-32Clock Selection3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Output Queue                                              | 3-18 |

| SCPI Conformance Information3-21Short Form Commands3-22Programming Guidelines3-28Overview3-28VXI Programming Requirements3-28Testing an Asynchronous Channel3-29Transmitting Data3-30Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-32Clock Selection3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Status Byte Register                                      | 3-18 |

| Short Form Commands3-22Programming Guidelines3-28Overview3-28VXI Programming Requirements3-28Testing an Asynchronous Channel3-29Transmitting Data3-30Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-32Clock Selection3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Saving the Enable Register Values                         | 3-20 |

| Programming Guidelines3-28Overview3-28VXI Programming Requirements3-28Testing an Asynchronous Channel3-29Transmitting Data3-30Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-32Clock Selection3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SCPI Conformance Information                              | 3-21 |

| Overview.3-28VXI Programming Requirements.3-28Testing an Asynchronous Channel3-29Transmitting Data.3-30Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation.3-32Clock Selection3-33Timing Pulse Output3-33Chapter 4.4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Short Form Commands                                       | 3-22 |

| VXI Programming Requirements.3-28Testing an Asynchronous Channel3-29Transmitting Data.3-30Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation.3-32Clock Selection3-33Timing Pulse Output3-33Chapter 4.4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Programming Guidelines                                    |      |

| Testing an Asynchronous Channel3-29Transmitting Data3-30Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-32Clock Selection3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Overview                                                  |      |

| Transmitting Data.3-30Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-32Clock Selection3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VXI Programming Requirements                              | 3-28 |

| Receiving Data3-31Receiving Messages with an EOM Character3-32SDLC Mode Operation3-32Clock Selection3-33Timing Pulse Output3-33Chapter 44-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Testing an Asynchronous Channel                           | 3-29 |

| Receiving Messages with an EOM Character       3-32         SDLC Mode Operation       3-32         Clock Selection       3-33         Timing Pulse Output       3-33         Chapter 4       4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Transmitting Data                                         | 3-30 |

| SDLC Mode Operation       3-32         Clock Selection       3-33         Timing Pulse Output       3-33         Chapter 4       4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Receiving Data                                            | 3-31 |

| Clock Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Receiving Messages with an EOM Character                  | 3-32 |

| Timing Pulse Output    3-33      Chapter 4    4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SDLC Mode Operation                                       | 3-32 |

| Chapter 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Clock Selection                                           | 3-33 |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Timing Pulse Output                                       | 3-33 |

| THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Chapter 4                                                 | 4-1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | THEORY OF OPERATION                                       | 4-1  |

| What's In This Chapter                       |      |

|----------------------------------------------|------|

| Basic Operation                              |      |

| 6075 Block Diagram Description               |      |

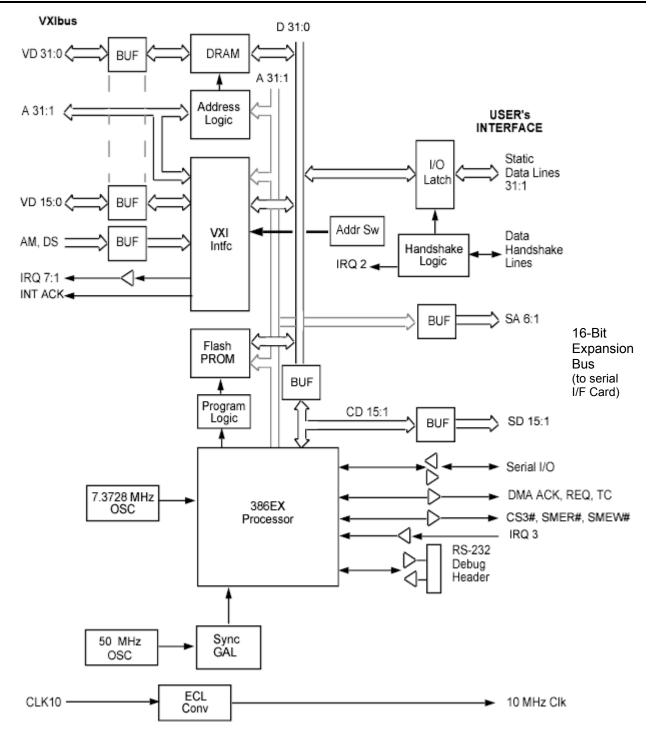

| VXI-Interface Card Description               |      |

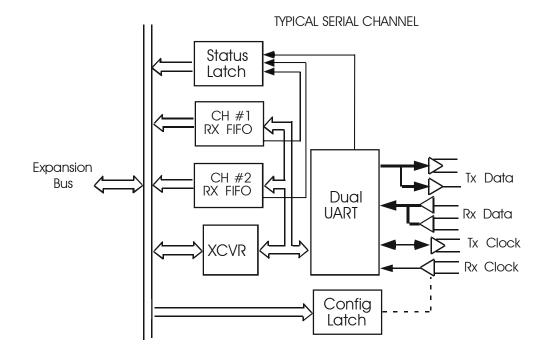

| Serial Interface Board                       |      |

| Chapter 5                                    |      |

| MAINTENANCE AND PERFORMANCE CHECKS           | 5-1  |

| Maintenance Overview                         | 5-1  |

| Troubleshooting Procedures                   |      |

| Self Test Failures                           |      |

| Troubleshooting Guide                        |      |

| Chapter 6                                    |      |

| PRODUCT SUPPORT                              |      |

| Product Support                              |      |

| Reshipment Instructions                      |      |

| Support Offices                              |      |

| Appemdix A                                   | A-1  |

| VXIBUS FDC ADDENDUM                          | A-1  |

| Introduction                                 | A-1  |

| Description                                  | A-1  |

| Background Information                       | A-2  |

| Fast Data Channel Advantages                 | A-2  |

| Fast Data Channel Usage on the 6075          | A-3  |

| Transmit Channels                            | A-4  |

| Receive Channels                             | A-5  |

| Fast Data Channel (FDC) Memory Map           | A-5  |

| Channel Memory Maps                          | A-5  |

| Fast Data Channel Buffer Definitions         | A-7  |

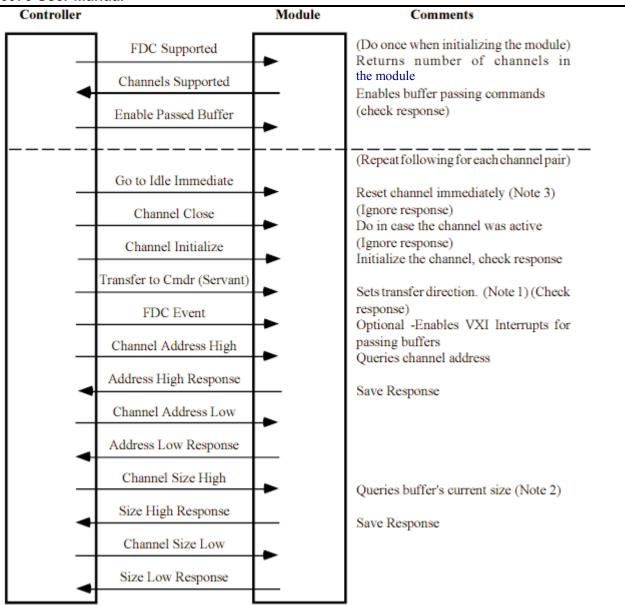

| Fast Data Channel Initialization Sequence    | A-8  |

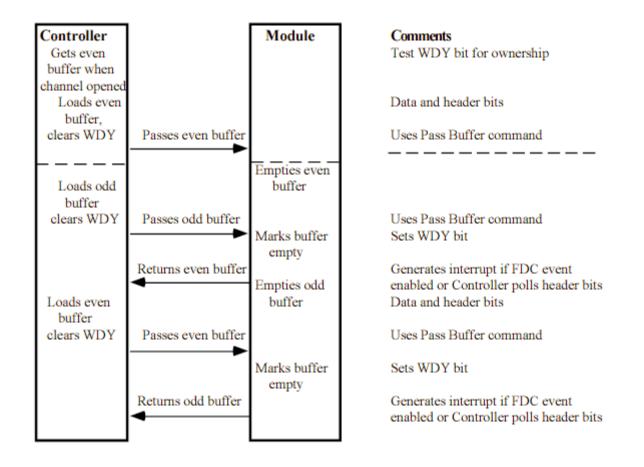

| Fast Data Channel Passing Sequence           | A-10 |

| Transfer to Servant                          | A-10 |

| Transfer to Commander                        | A-11 |

| FDC Command Reference                        | A-12 |

| Fast Data Channel (FDC) Command Summary      | A-12 |

| Fast Data Channel (FDC) Command Descriptions | A-13 |

| Channel Address Commands                                         | A-14 |

|------------------------------------------------------------------|------|

| Channel Size Commands                                            | A-15 |

| Fast Data Channel Events (Interrupt Response)                    | A-23 |

| Expanded Fast Data Channel Events (Interrupt Response)           | A-23 |

| Example Software Using FDC                                       | A-24 |

| Example #1: Transmit Data Using FDC                              | A-24 |

| Example #2: Open a Receive Channel to Begin Receiving Characters | A-27 |

| Example #3: Transmit Using Double Transmit Buffers               | A-28 |

| Example #4: Transmit and Receive From One or Two Channels        | A-31 |

| Example #5. Transmit and Receive With SDLC Format                | A-37 |

#### LIST OF FIGURES

| Figure 1-1  | Model 6075                                    | 1-1  |

|-------------|-----------------------------------------------|------|

| Figure 2-1  | Address Switch Location                       |      |

| Figure 2-2  | Address Switch Layout                         |      |

| Figure 2-3  | 6075 VXI Identification Label                 |      |

| Figure 2-4  | DTE 9 Pin to 25 Pin Adapter                   |      |

| Figure 3-1  | Display Mode Button Location                  |      |

| Figure 3-2  | VXI Status Register Bit Assignments           |      |

| Figure 3-3  | FDC Buffer Layout for 16-Bit Words            |      |

| Figure 3-4  | FDC Buffer Layout for 32 Bit Words            | 3-11 |

| Figure 3-5  | Status Reporting Structure                    | 3-15 |

| Figure 3-6  | Serial Controller Status Word                 | 3-33 |

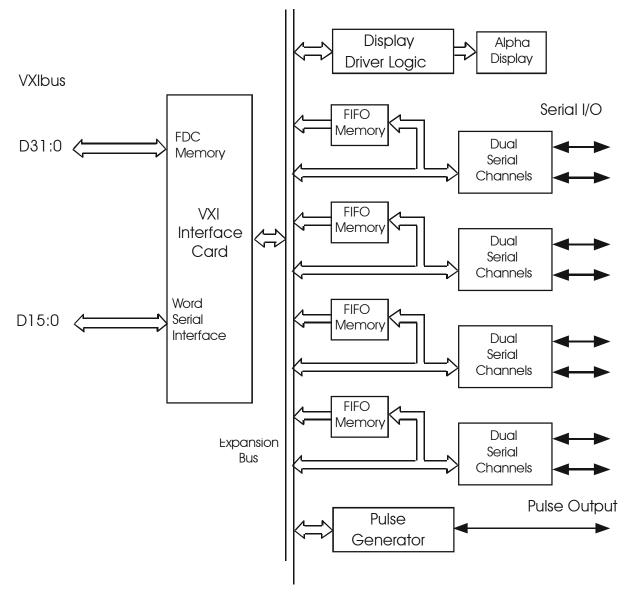

| Figure 4-1  | 6075 Simplified Block Diagram                 |      |

| Figure 4-2, | VXI Interface Card Block Diagram              |      |

| Figure 4-3, | VXI 6075 Serial Interface Board Block Diagram |      |

| Figure A-1  | Recommended FDC Initialization Sequence       | A-9  |

| Figure A-2  | Transfer to Servant Buffer Passing Sequence   | A-10 |

| Figure A-3  | Transfer to Commander Buffer Passing Sequence | A-11 |

## LIST OF TABLES

| Table 1-1  | VXIBus Glossary                                                    | 1-7  |

|------------|--------------------------------------------------------------------|------|

| Table 1-2  | Supported Instrument Protocols                                     | 1-10 |

| Table 1-3  | FDC Channels                                                       | 1-11 |

| Table 1-4  | STB and ESR response Bytes                                         | 1-11 |

| Table 1-5  | 6075 Default Parameter Settings                                    | 1-13 |

| Table 2-1  | Serial Interface Pin Assignments for Four Channel Units            | 2-6  |

| Table 2-2  | Serial Interface Pin Assignments for Eight Channel Units           | 2-8  |

| Table 3-1  | 6075 Display Modes                                                 | 3-3  |

| Table 3-2  | Normal Display Mode Messages                                       | 3-3  |

| Table 3-3  | Extended Mode Messages                                             | 3-4  |

| Table 3-4  | TEST Mode Messages                                                 | 3-4  |

| Table 3-5  | ERROR Messages                                                     | 3-4  |

| Table 3-6  | 6075 Word Serial Commands                                          | 3-9  |

| Table 3-7  | IEEE 488.2 Command List                                            | 3-20 |

| Table 3-8  | Recommended ESE And SRE Bit Values                                 | 3-20 |

| Table 3-9  | 6075 SCPI Command Tree - Asynchronous Mode                         | 3-24 |

| Table 3-10 | SCPI Command Reference                                             | 3-27 |

| Table 5-1  | Troubleshooting Guide                                              | 5-3  |

| Table A-1  | 16-Bit Wide FDC Memory Map                                         | A-6  |

| Table A-2  | 32-Bit Wide FDC Memory Map                                         | A-6  |

| Table A-3  | Fast Data Channel Standard and Racal Instruments Expanded Commands | A-12 |

## Chapter 1 GETTING STARTED

## What's In This Chapter

This chapter contains a general description of the VXIbus Models 6075-4, 4-Channel and 6075-8, 8-Channel Serial Communications Modules along with an overall functional description of the instruments. It lists and describes various options available for this model. It also describes the Model 6075 front panel connectors and indicators.

#### NOTE:

This manual provides a complete description of all features and options available with the Model 6075 however, some items described in the following paragraphs may not be installed in your instrument.

Figure 1-1, Model 6075

## Introduction

The Model 6075 is a single slot, C-size VXI module with four or eight independent serial channels for transmitting and receiving serial messages or data. Any or all of the serial channels can be active at the same time. Data transfer between the 6075 and the VXI controller is via VXI Fast Data Channels to minimize VXIbus transfer time and assure continuous data flow when operating at high baud rates. Each channel has two modes of operation: Asynchronous and SDLC.

The Asynchronous mode handles asynchronous data characters like those sent from a PC COMM port or from a CRT terminal. Asynchronous characters have a start bit, data bits, an optional parity bit and a stop bit. Messages are composed of one or more characters and do not have a character limit. Baud rates can be individually programmed for each channel in standard baud rates from 50 baud up to 460.8 Kbaud. The module generates nonstandard baud rates by dividing down from 460,800 Hz and selecting the closest divider ratio for the commanded rate.

The SDLC mode transmits data bytes in packets with a CRC checksum. SDLC characters have 8 data bits and no start or stop bits. The 6075's SDLC packet can hold from 2 to 30 data bytes. The packet size is set by the Frame:Size command. The SDLC packet format is:

Start byte Data Bytes CRC Bytes End byte

SDLC data rates can be up to 1 MB/s. The transmit 1X clock is normally transmitted with SDLC data. The data from each received packet is placed in the FDC data buffer and is immediately followed by the 16-bit status byte from the channel's UART. The status byte contains information about the packet and identifies the packet as being a good or bad packet. The 6075 module is a Message Based I4 class VXI instrument with interrupter capability and supports all of the required VXIbus Word Serial Commands under the VXIbus Specification VXIbus-1, Rev. 1.4. Control and setup commands are Word Serial Messages and Word Serial Commands. Serial data is normally sent and received via Fast Data Channel buffers in A32 address space. Test messages can be sent and received as Word Serial Messages. The 6075 should only be used with a Slot 0 Controller that supports the A32 address space.

The data input and output FDC channels operate as A/B buffer pairs and in Stream Transfer mode for enhanced throughput. Each channel uses two FDC buffers for transmit and two for receive. This makes a total of thirty-two FDC channels used to transfer the serial data over the VXIbus. The 6075 module supports Fast Data Channel (FDC) data transfer per VXIbus Specification VXIbus-10, Rev. 2.10 using the Standard FDC Word Serial Commands and an expanded command set that handles up to 32 FDC channels. In addition the module supports SCPI commands (1994.0) and IEEE Std 488.2-1987 commands.

## VXIbus Description

**VXIbus Objectives** The goal of the VXIbus Consortium is to create an open industry standard for modular instruments by defining interoperability between vendors, mechanical and environmental requirements, EMC compatibility, system initialization and software communication protocols. The physical portion of the VXIbus specification was adapted from the existing VME bus specification (IEEE-STD 1014). VXI is an acronym for "VME bus Extensions for Instrumentation."

The VXIbus specification details the technical requirements of VXIbus compatible components such as mainframes, backplanes, power supplies and modules. The specification also provides for interconnecting and operating different manufacturers' products within the same chassis. At the time of this publication, the current revision of the specification is version 2.0. The success of the specification is evidenced by over 300 manufactures who make over 800 different VXIbus products and hundreds of users .

The IEEE Standards Committee, in its IEEE-STD 1155, has adopted the VXIbus consortium's specifications. The U. S. Air Force has also accepted the specifications as the basis for its Modular Automatic Test Equipment (MATE) Instrument on a Card (IAC) standard. The VXIplug&play Alliance has defined several additional standards that simplifies the integration of multi-vendor VXI systems. The VXIplug&play Alliance has created a standard system framework concept that allows test programs in any language and operating system to be able to control VXI chassis and instrument modules through Standard Instrument Drivers. The VXIplug&play Framework identifies the operating system (OS) and applications development environment (ADE) used to generate the test software. The VXIplug&play Alliance just adopted an updated specification for a set of standard VISA Transition Library drivers that the Slot 0 Controllers and Embedded Computer vendors should adhere to assure VXIplug&play compatibility. The VISA (Virtual Instrument Software Architecture) drivers are used between the end user's test application program or general purpose test programs purchased from software vendors and the physical VXI modules or GPIB instruments. The VISA I/O library and full VISA drivers are described in the VXIplug&play VPP-4.2 Specifications.

## Advantages of VXIbus Based Systems

The VXIbus provides the user with the following advantages:

- Higher density packaging

- Increased system throughput

- More precise timing and device synchronization

- Standard protocols for instrument communication and control

- Ability to utilize existing VME modules

- Lower costs due to shared resources.

## VXIbus System Configurations

VXIbus systems utilize a chassis with a backplane and a common power supply. Modules plug into the chassis from the front and communicate to each other over the backplane. The left most slot in each chassis is labeled slot 0 and it is reserved for the system or chassis controller. Modules in the other slots are servants to the system controller but can also be controllers and have their own servants. The Slot 0 controller must be capable of performing the resource manager function which initializes the other modules and assigns logical addresses for dynamically addressed devices, interrupt lines, and trigger lines. The Slot 0 controller may be an embedded computer or it may simply be a translator module driven by an external computer.

Each VXI device is addressed by its logical address. The address may be static and preset by the user or dynamic and set by the resource manager function during system initialization. The VXIbus specification allows for 256 logical addresses. Address 0 is reserved for the Slot 0 controller and address 255 is reserved for dynamic addressable devices that will have their address defined by the resource manager. A VXI system can contain a maximum of 254 logical devices.

A module may be a single logical device or contain multiple logical devices. Physically the module can also be one slot wide or occupy multiple slots. Full rack wide VXI chassis have 13 slots on a 1.2 inch centers and can hold up to 13 one slot wide modules. Chassis extenders allow multiple chassis to be interconnected together producing systems of up to 254 logical devices.

VXI based systems can also incorporate non-VXIbus devices. The most common variations are the inclusion of GPIB instruments in the system or the use of VME cards in the VXI chassis. Slot 0 controllers commonly have a GPIB interface for controlling the GPIB instruments so that their operation can be controlled from the same program as are the VXI modules. VME cards can function in a VXI chassis because the VXIbus Specification maintained compatibility with the VME bus by retaining the VME signals definitions for P1 and the center row of P2. Provisions were also made to address the registers in the VME modules just as they are currently addressed in a VME bus system.

| Data Transfer<br>Methods                      | VXI modules can be register or message based . Register<br>based modules are typically controlled by direct reads or writes<br>to registers in the module. Message based modules<br>communicate with word serial messages that are strings of<br>ASCII or binary bytes. Word transfer uses the VXI word serial<br>protocol that examines bits in the modules's response register to<br>maintain an orderly data transfer. Because of the word serial<br>protocol, register based modules are typically faster than<br>message based modules but they lack the intelligence of<br>message based modules. A new Fast Data Channel<br>specification, VXI-1, provides for direct transfer of data from a<br>module's memory to the Slot 0 Controllers at rates up to 32<br>Mbytes per second. This allows smart message based modules<br>to have the same high data transfer rates as do register based<br>modules. |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Additional<br>information about<br>the VXIbus | For additional information, contact the VXI Consortium for a copy<br>of the VXI specification and the VXI Fast Data Channel<br>specification. Contact the VXIplug&play Alliance for a copy of<br>the VISA specification or Racal Instruments for Application<br>Bulletins that describe various VXI applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

**Commander**: A VXIbus device that has VME bus master capability and may have VXIbus servants under it in the system hierarchy. A Commander may act as a Servant to another Commander. A Commander must be message based.

**Servant**: A VXIbus device (with or without VME bus master capability) that is under control of a Commander in the VXIbus system hierarchy. A Servant may also be a Commander to other Servants. A Servant may be either message or register based.

**Interrupt Handler**: The module in the VXIbus system that generates the hardware interrupt acknowledge for a particular VME interrupt level. In VXIbus, the software interrupt handler may or may not be on the same module as the hardware interrupt handler.

**Logical Address**: A unique 8 bit number (0-255) which identifies each VXIbus device in a system. It defines the device's A16 register addresses.

**Resource Manager**: A message based commander located at logical address 0 which provides configuration management services, including address map configuration, Commander/Servant mapping, self test, and diagnostic management.

**VXI Message Based Instrument**: An intelligent instrument that implements the defined VXIbus registers and, at a minimum, word serial protocol.

**VXI Word Serial Messages**: The simplest required communication protocol supported by Message Based devices in a VXIbus system. It utilizes the A16 communications registers to transfer data or commands as a series of characters on the VXIbus backplane. The end bit is asserted on the last character of the message. Uses Word Serial Commands: Byte Available and Byte Request.

**VXI Word Serial Commands**: Single word, 16-bit commands sent from the commander to its servants. Some Word Serial Commands have a response word. The VXI specification defines a number of standard Word Serial commands that are reserved for use by the Slot 0 Controller or the Resource Manager. The specification also allows instrument designers to define their own Word Serial Commands.

**VXI Commands**: These are commands passed from a Commander to a Servant within the VXIbus environment. There are three broad categories of commands: VXIbus Instrument Protocols, IEEE 488.2 Common Commands, SCPI commands, and Device specific commands. A command may or may not be stimulated by an external event. For example an IEEE-488 Group Execute Trigger will generate a trigger command to all addressed devices. However, a Begin Normal Operations command is generated by the VXIbus resource manager and has no external source.

**VXI Events**: VXIbus Events are passed from a Servant to a Commander. They may be generated by the Servant either in response to a command (e.g., an invalid command error), or due to an external condition (e.g., data ready or status change).

VXI Fast Data Channel: A method for exchanging data between a commander and a servant module that utilizes a minimum of handshaking to transfer data so that the data transfer rate approaches the theoretical VME bus transfer rate. Allows a commander access to portions of the device's memory or a registers in the A32 address space. Data transfer is unidirectional for each channel and can be D16 or D32 bit words. Multiple channels may be opened for each device using A/B channel pairs for continuous data transfer.

488-VXIbus Interface Device: An IEEE-488 to VXIbus Interface Device is a message based device which provides communication between the IEEE-488 bus and VXIbus instruments. Typically this function is included in the Slot 0 card for external control of the VXI chassis.

#### Table 1-1, VXIBus Glossary

## Safety Considerations

The Model 6075 has been manufactured according to international safety standards.

#### WARNING

Do not remove instrument covers when operating or when the chassis power cord is connected to the mains.

|                     | powe<br>but v               | ered-on instrum                                                         | intenance and repair of an opened,<br>ent should be avoided as much as possible,<br>y, should be carried out only by a skilled<br>e of the hazard involved.                    |

|---------------------|-----------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supplied            | The f                       | ollowing access                                                         | sories are supplied with each 6075 module.                                                                                                                                     |

| Accessories         | Qty.                        | Part No.                                                                | Description                                                                                                                                                                    |

|                     | 1<br>2<br>2                 | 980870<br>TBD<br>TBD                                                    | 6075 Instruction Manual.<br>DC-37S Mating Connector (6075-8 only)<br>DC Hood (6075-8 only)                                                                                     |

| Specifications      | These                       | e specifications                                                        | tions are listed in the paragraphs below.<br>are the performance standards or limits<br>strument is tested.                                                                    |

| VXIbus Capabilities | The 6                       | 075 has the fol                                                         | lowing VXIbus capabilities:                                                                                                                                                    |

|                     | Addre                       | essing                                                                  | Static configured addresses 1-254 or<br>Dynamic configuration                                                                                                                  |

|                     | Devic                       | facturer ID<br>æ Class<br>æss Space                                     | 4091 decimal (Racal Instruments)<br>Message based I4 class VXI instrument<br>A16 (D16) / A32 (D32)<br>64 bytes in A16 space                                                    |

|                     | Mode                        | l Code                                                                  | 1 or 4 Mbytes in A32 space<br>12 bits, 607 decimal for Model 6075-4<br>608 decimal for Model 6075-8                                                                            |

|                     | FDC<br>Resp<br>VMEt<br>Comr | t Generator<br>Event Generato<br>onse Generator<br>ous Master<br>nander | D16, Programmable Interrupter<br>Programmable, Interrupts only<br>or Programmable, Interrupts only<br>r Not Supported<br>Not Supported<br>Not Supported                        |

|                     | Hand                        | ll Register<br>shake                                                    | Not Supported<br>Normal handshake only                                                                                                                                         |

|                     | Fast I                      | Data Channel                                                            | A32 (D32) Random Access,<br>16 Channels: I/O Pair & Stream Transfer<br>mode,<br>Standard FDC Word Serial Commands<br>and Expanded FDC Word Serial<br>Commands per FDC Addendum |

|                     | Prima                       | Transfer Rate<br>ary<br>ification                                       | approximately 4 Mbytes per second                                                                                                                                              |

|                     |                             |                                                                         |                                                                                                                                                                                |

## VXIbus Instrument Protocols